KIST, 3차원 초미세 패턴 기술 개발…"차세대 반도체칩 적용 기대"

|

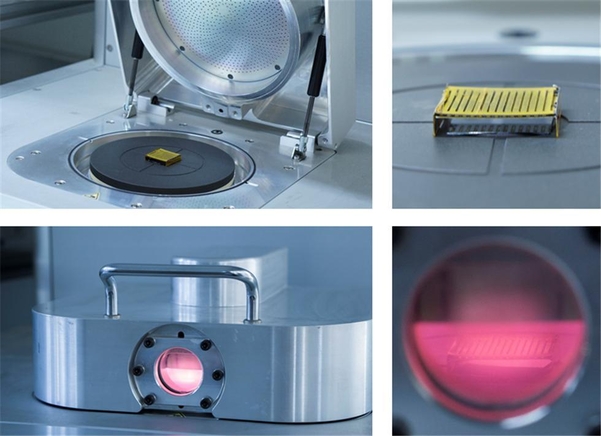

| 한국과학기술연구원 연구진이 실험에 사용한 플라즈마전용 필터와 필터를 도입한 플라즈마 공정. /사진=한국과학기술연구원 제공 |

국내 연구진이 차세대 반도체에 활용할 수 있는 3차원 초미세 패턴 기술을 개발했다.

한국과학기술원(KIST)은 21일 광전하이브리드연구센터 손정곤 박사팀이 반도체 칩이나 광전소재 제조에 사용되는 '나노 패터닝(Nano Patterning)'을 한 차원 높인 기술 개발에 성공했다고 밝혔다.

손 박사팀이 개발한 기술은 다양한 '블록공중합체(Block Copolymer)에 적용 가능한 10나노미터(1억분의 1미터) 이하의 초미세 나노 패턴 제작 공정이다. 블록공중합체는 두 개 이상의 고분자가 하나의 고분자 사슬에 규칙적으로 연결된 고분자를 뜻한다.

최근 차세대 반도체를 위한 공정으로 10 나노미터 이하 초미세 패턴 제작 기술이 각광받고 있다. 이 기술을 활용하면 삼성전자 등이 차세대 반도체 공정으로 활용 중인 극자외선(EUV) 공정과 달리 저렴하고 빠르게 넓은 면적의 초미세 나노 패턴을 얻을 수 있다는 게 연구진의 설명이다.

손 박사팀은 이 기술을 통해 실제 반도체 공정에서 3차원 입체구조 트랜지스터로 사용되는 핀펫(FinFET)을 모사한 3차원 구조를 구현할 수 있었다. 더불어 미세화학 패턴 위에서도 결함이 거의 없는 10나노미터 이하 수직 줄무늬 패턴을 형성할 수 있다는 점도 입증했다.

손정곤 박사는 "이번 10나노미터 이하 패터닝 기술이 초미세 반도체 공정 기술로 실제 적용되길 기대한다"고 전했다.

한편 이번 연구는 과학기술정보통신부 지원으로 KIST 기관고유사업과 한국연구재단 중견연구자지원 사업으로 수행됐다. 연구결과는 과학저널인 네이처의 자매지 '네이처 커뮤니케이션즈' 최신호에 게재됐다.

박소영 머니투데이방송 MTN 기자